Students earn two awards at ISPD Gate Sizing Contest

Enlarge

Enlarge

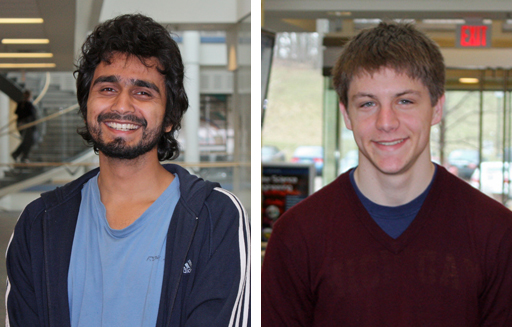

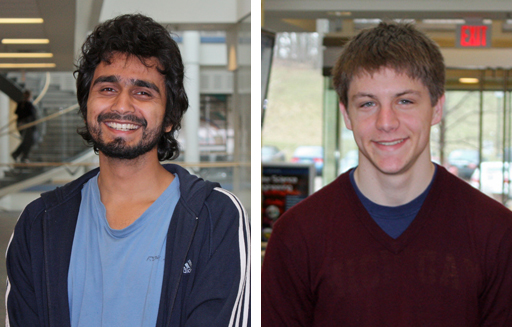

Team Trident, a student team composed of U-M CSE graduate student Pankit Thapar and CS undergraduate Benjamin Vandersloot, along with UCSD students Seokhyeong Kang and Hyein Lee, has won two awards in the 2013 ISPD Discrete Gate Sizing Contest, which took place on March 27 at the ACM International Symposium on Physical Design. The team, coached by Prof. Igor Markov and by Prof. Andrew Kahng at UCSD, placed first in secondary metric category and second in the primary metric category.

The annual ISPD design contest challenges teams from around the world to advance the state-of-the-art, which in past years has focused on faster circuits and more compact semiconductor layouts. The contest traditionally focuses on a specific type of challenge for two years in a row, and in 2013, the contest was the second in a pair of challenges focused on discrete gate-sizing for lower-power operation. The contest was sponsored with support from Intel, Cadence, and Synopsys.

Specifically, the 2013 contest focused on gate-sizing and threshold voltage assignment for a given circuit to achieve the lowest possible operating power that still satisfied performance constraints. Intel researchers substantially extended their infrastructure used for the ISPD 2012 contest, so as to evaluate both gate and interconnect delay, and checked capacitance and slew constraints (in addition to full-netlist timing constraints). Total runtime per benchmark was limited, with tighter limits in a secondary category, where tool runtime could be traded off for leakage power.

Circuit timing was evaluated by an industry-standard signoff timing software provided by Synopsys. This challenged researchers in the field who are used to closed-form analytical circuit delay models. The use of parallel computing was encouraged and contestants were allowed to use up to 16 parallel hardware threads on evaluation servers at Intel. To exploit these computational resources, Team Trident developed a multithreaded stochastic combinatorial optimization framework that successfully handled circuits with 0.98 million gates during the final stage of the contest, as well as an internal timing analysis tool that erred by single picoseconds (on average) compared to the industry signoff timer.

25 engineering teams from eight different countries competed, and of those nine completed submissions to the final evaluation phase. Team Trident placed second for the primary metric,which evaluated circuit power, subject to various constraints. The team placed first for the second metric, which combined circuit power and optimization runtime, encouraging contestants to strike the best tradeoff. The contest and results summary document (PDF) from the contest provides additional detail.

Read More:

MENU

MENU